A highly optimized 22FDSOI Logic Architecture for Power, Performance, Area (PPA) and cost is presented. Unique features of FDSOI technology including channel strain based PFET transistor performance enhancement are further advanced with innovative low cost MOL/BEOL based special constructs. The new constructs allow a highly optimized continuous active PFET transistor based (CNRX) library design. Based on this architecture, PPA advantage is demonstrated over competing bulk and FinFET technologies. In addition, design and implementation of Body-Bias Generator (BBGEN) for Forward Back-Bias (FBB) operation of transistor devices in 22FDX Fully Depleted Silicon-On-Insulator (FD-SOI) process. This architecture has also been implemented for on demand device trimming applications to enhance the performance of slow devices towards faster corner by the application of Threshold Voltage (VT) tuning using FBB. The technology is also tuned to operate at near-Threshold as well as optimized for edge AI applications with further enhancement of library and special logic & memory based synthesizable unit called SLM (Synthesizable Logic memory).

Hosted by the MIT AI Hardware Program and the Microsystems Technology Laboratory.

Speaker

Navneet Jain

Navneet Jain is a Distinguished Member Technical Staff at GlobalFoundries, Inc, Santa Clara, since 2009. He holds a PhD and MTech in EE form IIT Delhi, India and BE(Hons) in EEE from BITS Pilani, India. He has over 25 years of experience in the field of circuit/logic design, optimization and methodologies for timing closures for microprocessor and graphics chip design at SGI, Transmeta, AMD, SGI, Software &Technologies (Duet) and Center for Applied Research in Electronics (CARE) at IIT Delhi. At GlobalFoundries he has architected and productized standard cells libraries in 22FDX, 12LPP, and 45SPCLO including several test chips for FAB silicon validations with emphasis on developing ultra-lower and low leakage design. Navneet has over 20 patents and 10 publications in IEEE transactions and international conferences.

Explore

MIDDAS: Memory Integration and Data Dis-Aggregation

Wednesday, November 19, 2025 | 12:00 - 1:00pm ET

Hybrid

Zoom & MIT Campus

New 3D Chips could Make Electronics Faster and more Energy-Efficient

Adam Zewe | MIT News

The low-cost, scalable technology can seamlessly integrate high-speed gallium nitride transistors onto a standard silicon chip.

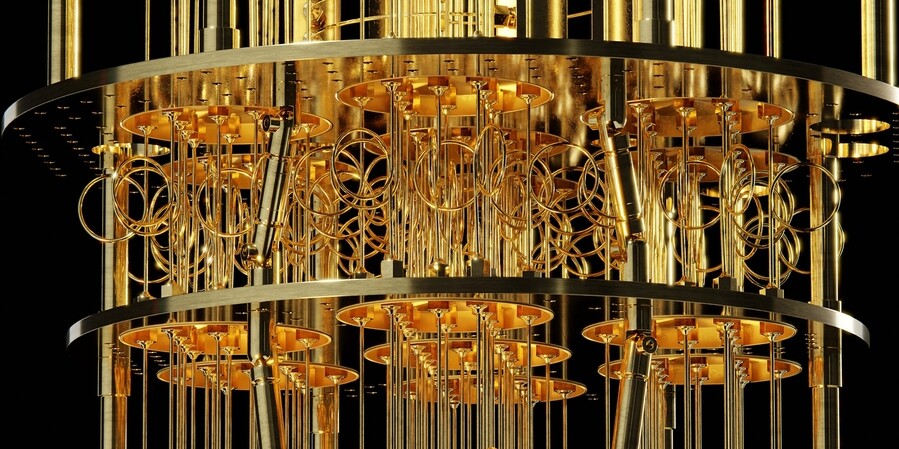

Closing in on Superconducting Semiconductors

Julianna Mullen | Plasma Science and Fusion Center

Plasma Science and Fusion Center researchers created a superconducting circuit that could one day replace semiconductor components in quantum and high-performance computing systems.